# Real-time Software Architectures and Performance Evaluation Methods for 5G Radio Systems

#### Dissertation

submitted to

#### Sorbonne Université

in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Author:

#### Tsu-Han WANG

Scheduled for defense on the 13th December, 2022, before a committee composed of:

Reviewers

Dr. Thierry Turletti INRIA, France

Prof. Ludovic Apvrille Télécom Paris, France

Examiners

Prof. Melek Önen EURECOM, France Prof. Ternying Hsu NCTU, Taiwan

Director of Thesis

Prof. Raymond KNOPP EURECOM, France

# Architectures logicielles temps-réel et m'éthodes d'évaluation des performances les systèmes radio 5G

Thèse

soumise à

Sorbonne Université

pour l'obtention du Grade de Docteur

Auteur:

Tsu-Han WANG

Soutenance de thèse effectuée le 13 Decembre 2022 devant le jury composé de:

Rapporteurs

Dr. Thierry Turletti INRIA, France

Prof. Ludovic Apvrille Télécom Paris, France

*Examinateurs*

Prof. Melek Önen EURECOM, France Prof. Ternying Hsu NCTU, Taiwan

Directeur de Thèse

Prof. Raymond KNOPP EURECOM, France

### Abstract

Cette thèse a pour sujet l'optimisation de la radio logicielle (SDR, software defined radio) pour la 5G. Le premier point à aborder est la radio logicielle. Comme son nom l'indique, la radio logicielle est un programme informatique qui est exécuté par un ordinateur se comportant comme une station radio. Ce qui rend ce système particulier c'est qu'il sagit d'un logiciel, avec toutes les caractéristiques d'un logiciel, mais qui exécute ce qui jusqu'alors était réservé au matériel. Plusieurs raisons expliquent la popularité croissante de la radio logicielle. L'une d'elles est que la conception d'une puce électronique est longue et tolère peu les erreurs. Pour produire une puce électronique, il faut tout d'abord passer par une étape de conception utilisant un langage de bas niveau de type Verilog pour décrire le comportement du système. Ensuite ce programme doit être traduit en un graphique où la taille de chaque porte logique, comment elle est implémentée, et où elle est positionnée, sont importants puisque la taille de la puce a un impact direct sur son coût de fabrication. De même, les connections entre les portes de la puce doivent être soigneusement conçues puisque les longs chemins induisent des délais dans l'acheminement des données ce qui pourrait générer des erreurs. Et il ne s'agit là que d'un coup d'œil sur la conception de la puce dans la phase graphique. Après toutes ces étapes, ce graphique va à l'usine où la gravure sur puce réelle est effectuée. Il faut traverser le revêtement, graver la couche pour révéler le silicium, graver le silicium, et laver les résidus. Ces étapes ne servent à produire qu'une seule couche de la puce, qui en contient plusieurs. Cela montre bien qu'il faut du temps et de la précision pour fabriquer une puce. De tout ce qui précède, on peut dire que produire une puce est à la fois coûteux et long.

La radio logicielle bénéficie des avantages du développement logiciel, avec un cycle de vie de développement court et une facilité certaine pour ajouter de nouvelles fonctionalités. Cependant, des obstacles demeurent que la radio logicielle doit surmonter, le premier étant le temps réel. Les puces matérielles nécessitent toute cette complexité de conception pour s'assurer qu'elles peuvent traiter le signal de la manière la plus rapide possible. Les programmes informatiques qui tournent sur des ordinateurs à usage général ne peuvent pas égaler les performances des puces matérielle. La bonne nouvelle pour la radio logicielle est que les processeurs sont de plus en plus puissants avec les machines récentes donc même si les logiciels ne peuvent rivaliser en terme de performance avec le matériel, ils peuvent quand même gérer les procédures dans le temps imparti. De plus, malgré cet inconvénient de moindre performance, le logiciel a l'avantage évident d'avoir un cycle de développement court. Dès que de nouvelles fonctionalités doivent être ajoutées à la radio logicielle, il suffit simplement d'introduire une nouvelle fonction qui exécute cette

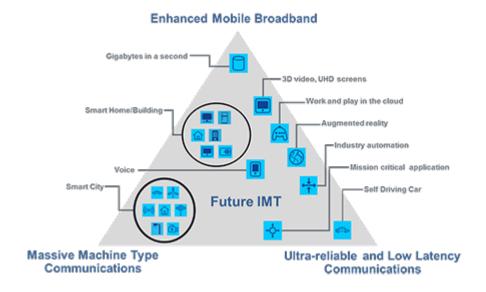

# Gigabytes in a second Smart Home/Building Work and play in the cloud Augmented reality Industry automation Smart City Future IMT Massive Machine Type Communications Ultra-reliable and Low Latency Communications

Figure 3 - IMT-2020

fonctionalité et de recompiler le programme. Et aussi, il peut prendre en charge plusieurs configurations car pour le programme, il ne s'agit que d'un ensemble de variables qui doivent être prédéfinies par la configuration. Donc au final, de plus en plus de gens s'intéressent à la radio logicielle en raison de sa souplesse de développement et tolèrent sa lenteur puisque les traitements sont quand même faits dans les temps.

Le deuxième point à aborder est la 5G. La 5G a trois caractéristiques principales qui sont le haut débit mobile amélioré (Enhanced Mobile Broadband, eMBB), les communications ultra-fiables et à faible latence (Ultra-reliable and Low Latency Communications, URLLC), et les communications massives de type machine (Massive Machine Type Communications, mMTC), comme le montre la figure 3. L'eMBB se concentre sur les débits de données massifs avec une large bande où la transmission de données est la principale préoccupation tandis que l'URLLC, de par son nom, se concentre d'avantage sur la précision et les réponses rapides pour des usages avec un besoin de rétroaction rapide, la conduite automatique par exemple. Quant à mMTC, il s'agit plus de gérer simultanément une quantité massive d'appareils sur une large portée où la quantité d'appareils gérés en même temps est la principale préocuppation, par exemple l'internet des objets (Internet of Things, IoT)

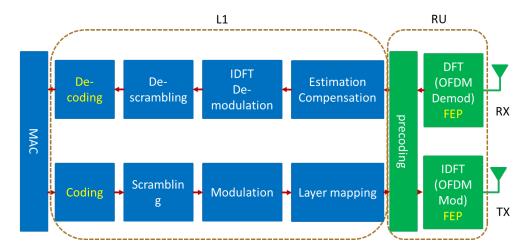

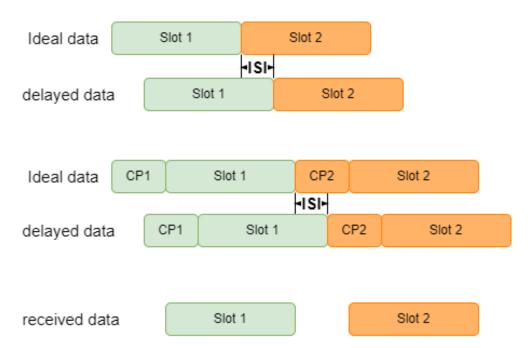

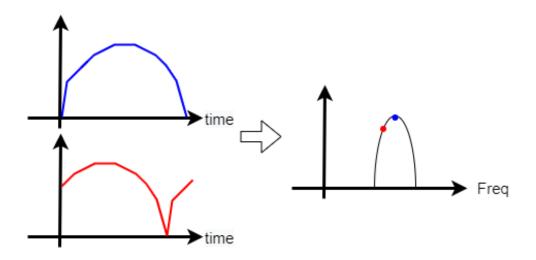

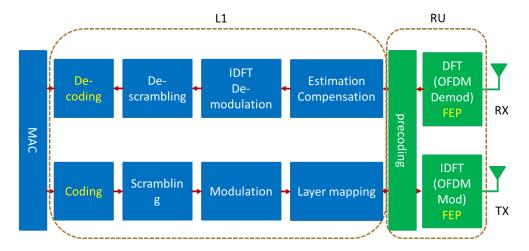

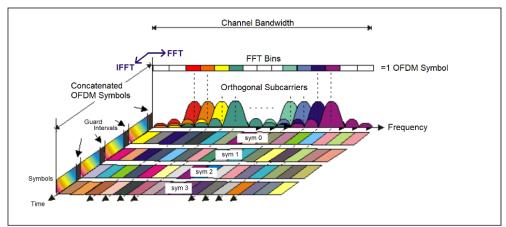

Ce qui précède decrit ce qu'est la radio logicielle 5G. Ce dont va traiter cette thèse est la couche physique (PHY). Il y a sept couches pour la connection internet et la couche physique est la plus basse de toutes. Ce que fait la couche physique c'est principalement de gérer le flux binaire et de transmettre et recevoir ce flux entre les appareils. Pour pouvoir parler de communication sans fil nous devons tout d'abord parler d'une des plus importantes conceptions dans le domaine des communications, le multiplexage par répartition orthogonale de la fréquence (Orthogonal Frequency-Division Multiplexing, OFDM). Le principe d'OFDM est d'avoir plusieurs porteuses dans le domaine fréquentiel

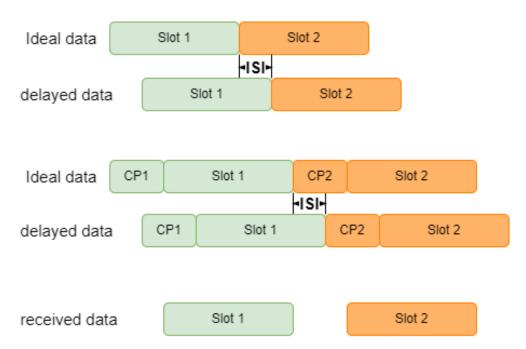

Figure 4 – Inter Symbol Interference (ISI)

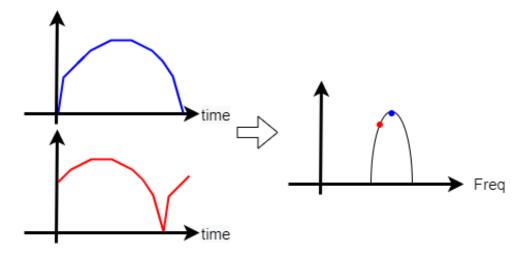

orthogonales pour transmettre les données. Ainsi, idéalement, il y aura des interférences seulement où ne se trouvent pas les données. Cependant en pratique, il existe toujours des interférences inter-symboles (Inter-Symbol Interference, ISI) et des interférences inter-porteuses (Inter-carrier Interference, ICI). ISI et ICI se produisent à cause du délai d'arrivée du paquet ce qui signifie qu'il y aura des données manquantes et/ou melangées dans le signal reçu. ISI peut se résoudre en ajoutant une période de garde contenant des données connues, par exemple du remplissage par des zéros, comme illustré par la figure 4. Bien que l'ajout de données connues résolve le problème ISI, cela ne résout pas l'ICI. L'introduction du préfixe cyclique (Cyclic Prefix, CP) au lieu d'un remplissage par des données connues résout le problème de l'ICI puisque le décalage temporel dans le domaine temporel n'est qu'un décalage dans le domaine fréquentiel, comme illustré à la figure 5, les données sont toujours récupérables.

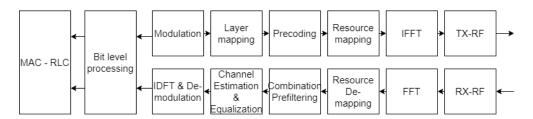

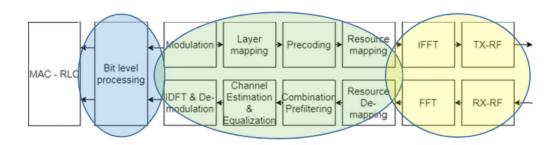

Étant donné que tout le travail de la procédure PHY vise à ce que le signal OFDM soit transféré et décodé avec succès même face à des interférences lors du passage dans le canal, ce dont PHY doit se préoccuper, c'est de savoir comment obtenir des données de flux binaire réversibles avec une tolérance pour les bruits. Prenons l'exemple de la transmission descendante (downlink). Les données de flux binaire proviennent de la couche supérieure et subissent ensuite un traitement au niveau du bit qui consiste en un brouillage et un codage. Le brouillage modifie l'ordre des données du flux binaire pour tenir compte des cas d'interférences en rafale qui perturbent les données consécutives. Quant au codage, il consiste à ajouter des bits de contrôle selon un algorithme de codage donné pour s'assurer que même si certains bits sont contaminés par le bruit, ils sont toujours récupérables. Et après le brouillage et le codage, vient la modulation

Figure 5 – Inter Carrier Interference (ICI)

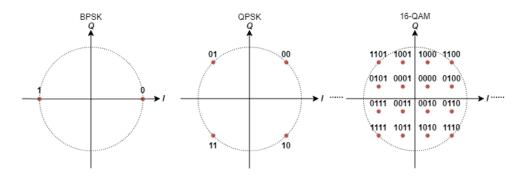

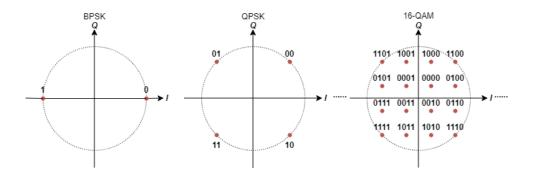

Figure 6 – Quadrature Amplitude Modulation (QAM) diagram example

d'amplitude en quadrature (Quadrature Amplitude Modulation, QAM). Ce que fait QAM, c'est mapper les données de flux binaires sur des ensembles d'amplitudes et d'angles afin qu'ils puissent être ajoutés à l'onde OFDM, comme illustré à la figure 6. Enfin il y a le mappage OFDM. Ce n'est que la procédure pour une couche et une antenne. Pour la 5G, il est nécessaire de disposer de plusieurs antennes pour prendre en charge les entrées multiples et les sorties multiples (Multiple-Input Multiple-Output, MIMO). Pour le fonctionnement MIMO, le mappage de plusieurs couches sur plusieurs antennes est effectué par mappage et précodage de couche pour s'assurer que chaque antenne a le signal qu'elle doit envoyer, puis on effectue la transformée de Fourier rapide inverse (Inverse Fast Fourier Transform, IFFT) pour répondre aux exigences OFDM.

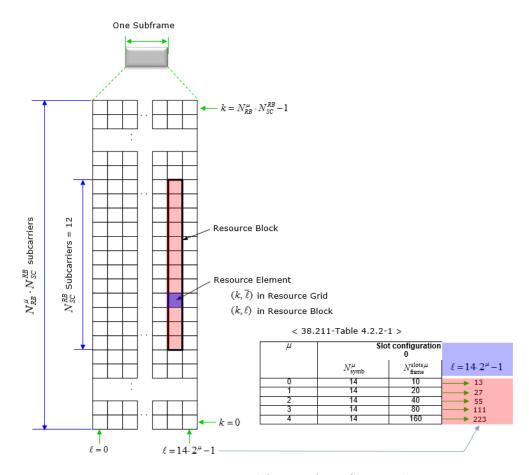

Comme mentionné précédemment, tous les processus doivent être faits « à temps », ce qui rend la contrainte de temps de plus en plus importante. Dans la norme 3GPP pour la 5G, la relation entre l'espacement des sous-porteuses et le slot est indiquée dans le tableau 1

Les équations suivantes montrent la relation entre l'espacement des sous-porteuses

| $\mu$ | $\Delta f = 2^{\mu} * 15[kHz]$ | Cyclic prefix    |

|-------|--------------------------------|------------------|

| 0     | 15                             | Normal           |

| 1     | 30                             | Normal           |

| 2     | 60                             | Normal, Extended |

| 3     | 120                            | Normal           |

| 4     | 240                            | Normal           |

Table 1 – Numérologie et espacement des sous-porteuses dans la norme 3GPP

et le slot où le slot est l'unité de temps de base dans PHY.  $T_c = 1/(\Delta f_{max} * N_f)$  où  $\Delta f_{max} = 480 * 10^3$ HZ et  $N_f = 4092$ , La constante  $k = T_s/T_c = 64$  où  $T_s = 1/(\Delta f_{ref} * N_{f,ref})$ ,  $\Delta f_{ref} = 15 * 10^3$ HZ et  $N_{f,ref} = 2048T_f = (\Delta f_{max}N_f/100) * T_c = 10ms$ . Ces équations montrent que le temps de trame est toujours de 10 ms, mais qu'il y aura plus de slots dans une trame lorsque la numérologie augmentera, ce qui signifie que le slot devient plus court tout en utilisant une numérologie plus grande. La numérologie zéro est la même configuration que celle utilisée par LTE où le slot est de 1 ms, ce qui signifie que le slot en 5G est généralement plus court que ce qui est demandé en LTE.

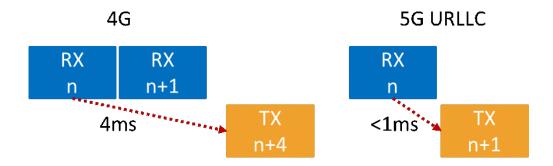

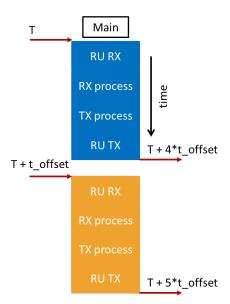

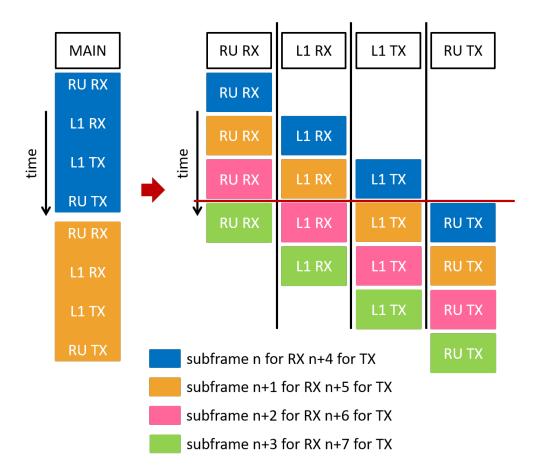

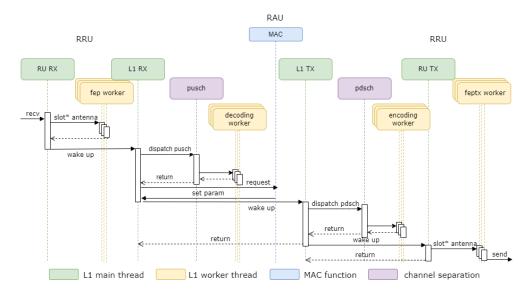

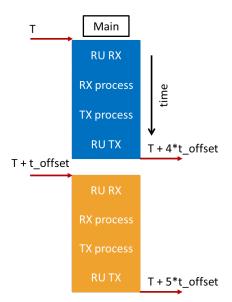

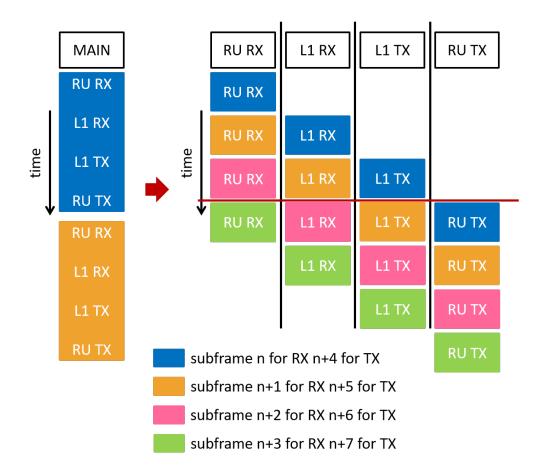

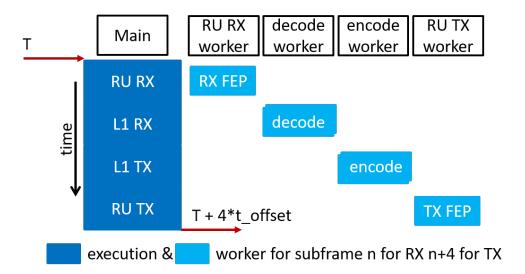

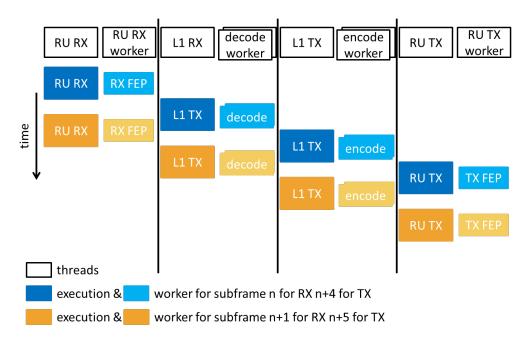

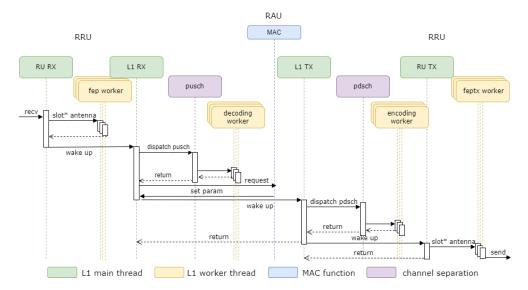

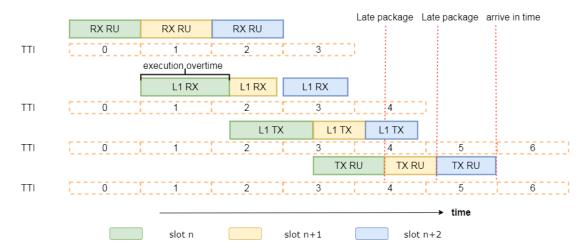

Connaissant la durée de l'unité de base, le slot, dans PHY, nous savons maintenant que le temps d'exécution de toutes les procédures du processus PHY, une fois tout additionné, doit être compris dans un slot pour que la radio logicielle s'exécute de manière stable. Il est alors important de savoir combien de temps coûte chaque fonction individuelle et combien de temps coûte l'ensemble de la procédure. Parlons d'exécution séquentielle. Ce qui est fait est de programmer la fonction PHY directement à partir de la norme 3GPP avec le même ordre de flux d'exécution, comme illustré à la figure 7. Et puisque le canal répond quatre slots plus tard dans le canal opposé, comme indiqué à la figure 8, on a instinctivement le fonctionnement suivant : traiter le slot n pour un côté (transmission ou réception), puis le côté opposé pour le slot n+4. Il est plus logique d'avoir le système piloté par la réception que par l'émission puisque le système doit activer la procédure de réception à chaque tranche de temps et ce n'est qu'à ce moment-là que les données sont connues pour la transmission. Pourtant, la transmission peut être pré-générée bien avant qu'elle ne soit transmise. Ce qui aboutit finalement à la structure décrite à la figure 9.

D'après la figure 9, on peut voir que la transmission est préparée bien plus tôt que ce qui est nécessaire, où le temps total d'exécution pour une réception et une transmission est preque le même que la durée d'un slot dans LTE quand il y a une forte charge. Avec un ordonnancement si serré, la préparation précoce des données transmises est considérée comme un gaspillage d'énergie et de ressources. Sans oublier qu'avoir un ordonnancement plus serré pour des slots plus courts en 5G rend cette structure peu pratique, que l'accélération doit améliorer. Il existe deux idées principales pour l'accélération. La première est de réorganiser la structure ce qui signifie avoir de multiples exécutions parallèles en même temps, par exemple « time space trading ». La deuxième est d'accélérer la fonction elle-même.

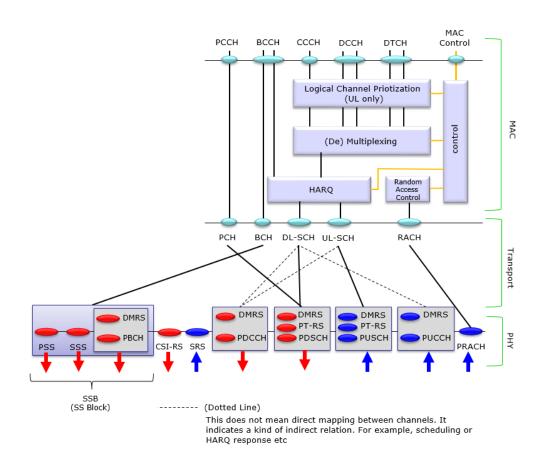

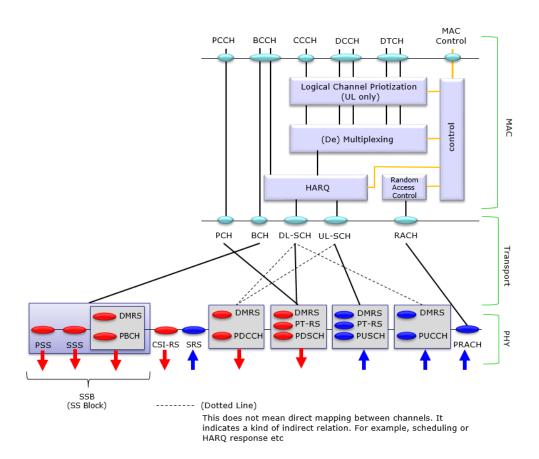

Premièrement, parlons de la réorganisation de la structure. Il est important de savoir que tous les canaux ont peu de relations les uns avec les autres comme illustré par la figure

Figure 7 – Flux de procédure PHY pour la radio logicielle

Figure 8 – Réponse du canal dans différents modes

Figure 9 – Procédure pour l'exécution séquentielle radio logicielle

10. Cela signifie que la plupart des canaux peuvent être traités en parallèle. Pourtant, le découpage du traitement des canaux en morceaux est un peu difficile à gérer, donc l'accent sera mis sur ceux qui consomment le plus de temps et de ressources, à savoir les canaux partagés, responsable de la majeure partie du transfert de données. Il y a deux canaux partagés, un pour la liaison montante et un pour la liaison descendante. En plus du traitement du canal, le traitement d'antenne OFDM coûtera également un peu de temps lors de l'utilisation de plusieurs antennes. Ainsi, les quatre principales parties chronophages sont la procédure OFDM pour la réception et la transmission et la procédure de canal partagé pour la réception et la transmission. Étant donné que l'ordre de ces quatre procédures est irréversible, nous devons proposer une structure qui conserve l'ordre tout en les exécutant en même temps. Bien que cela puisse sembler un peu contradictoire, il existe en fait une solution qui s'appelle un pipeline.

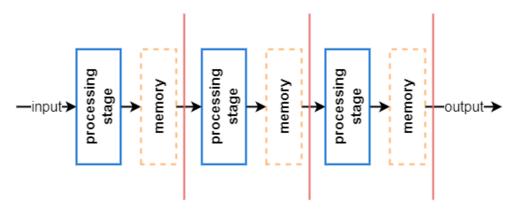

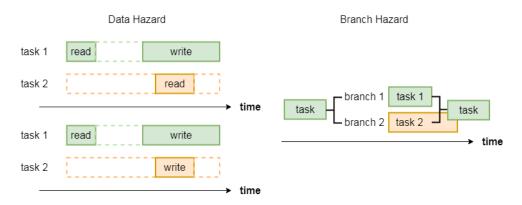

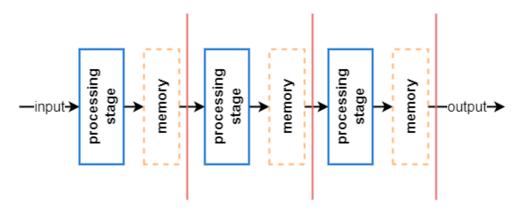

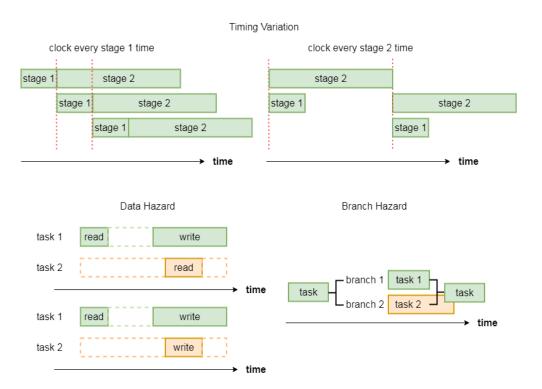

La structure de pipeline d'origine est illustrée à la figure 11. La structure de pipeline traditionnelle utilise une horloge globale qui déclenche les étapes pour démarrer le traitement, aux instants marqués par la ligne rouge sur la figure 11, mais il peut y avoir quelques problèmes. Le premier problème que l'on peut rencontrer est de diviser le processus de manière inégale, ce qui est une variation temporelle. Chaque étape du pipeline a son propre temps d'exécution qui est très probablement différent des autres puisque chaque étape a sa propre procédure unique. Si les temps d'exécution de chaque étape sont trop différents les uns des autres, cela signifie que le fractionnement de ce pipeline est déséquilibré, ce qui pourrait non seulement réduire le parallélisme du programme, mais également écraser les données de référence ou les données d'entrée pour l'étape suivante, comme indiqué dans la partie de la variation temporelle de la figure 10. Le deuxième problème est d'avoir un conflit de données. Le conflit de données est un autre problème qui peut survenir lors de l'utilisation de la programmation parallèle.

Figure 10 – Mappage des canaux - Share Tech<br/>Note  $\,$

Figure 11 – Un exemple de structure de pipeline à trois étages

Lorsqu'il y a plusieurs écritures qui se produisent en même temps ou lorsqu'une écriture et une lecture se produisent en même temps, l'ambiguïté de qui vient en premier a un impact énorme sur le résultat final. Ce type de risque sur les données rendra le programme instable, ce qui est définitivement indésirable dans la radio logicielle, comme indiqué dans la partie sur les risques sur les données de la figure 12. Le troisième type de problème qui peut survenir dans la programmation parallèle est le risque sur les branches. Si le programme exécute plusieurs branches en parralèle, au moment de la fusion de ces branches pour continuer le processus, il se peut qu'une partie des données ne soit pas encore prête à être gérée en fonction du moment où le processus fusionné est exécuté comme indiqué dans la partie risque sur les branches de la figure 12.

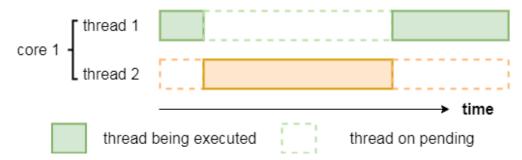

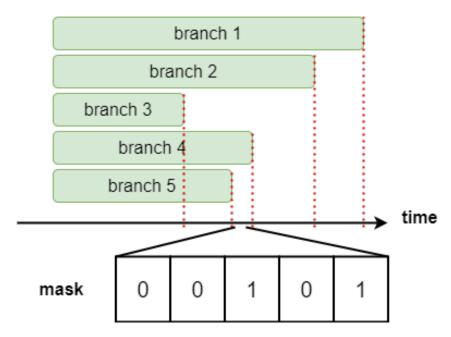

Ici, la structure du pipeline radio logicielle pourrait tirer parti d'une version logicielle où les threads sont responsables du parallélisme. Les threads sont utilisés dans la programmation parallèle car ils peuvent s'exécuter en même temps. En intégrant le pipeline dans une version logicielle, chaque thread représentera une étape de pipeline. Bien que la structure de pipeline d'origine ait été proposée pour la conception matérielle, les problèmes mentionnés précédemment resteront préoccupants après l'intégration de la structure de pipeline dans une version logicielle. Pourtant, le pipelining logiciel présente des avantages, car tous ces problèmes ont une solution plus simple dans une version logicielle où les risques sur les données peuvent être résolus en utilisant le verouillage mutex pour la tâche qui travaille actuellement sur les données. Et les tâches qui voudront également demander l'écriture devront attendre que la mémoire soit libérée puis le système des verrous donnera le droit d'écrire des données à une des tâches en attente, de manière équitable. En ce qui concerne le problème de fusion des branches, le plus important est de s'assurer que la tâche suivante ne commence à s'exécuter qu'une fois toutes les tâches de branche avant la fusion terminées. La solution utilisée dans cette thèse est d'avoir un masque binaire qui contient sa taille en bits qui est au moins de la même taille que le nombre de tâches de branche. Chaque bit du masque représente la branche correspondante et le masque est partagé entre toutes les branches. Une fois que la branche a terminé sa tâche, elle positionnera alors le bit correspondant dans le masque à un pour représenter qu'elle a terminé sa tâche. Chaque branche effectuera la

Figure 12 – Risque

vérification du masque et s'il ne reste plus de zéro réveillera la tâche suivante. La même méthode mentionnée ci-dessus pour la prévention des risques sur les données est utilisée pour résoudre les risques sur les branches lors du remplissage du masque. Cela signifie qu'une seule tâche peut remplir le masque à la fois pour s'assurer qu'il n'y aura pas de branches non suivies.

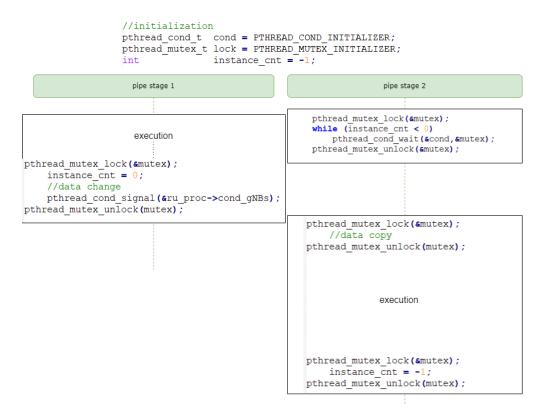

Dans le pipeline logiciel, le déclenchement par l'horloge est remplacé par le signal envoyé. Cela signifie qu'une étape du pipeline logiciel est réveillée par l'étape précédente plutôt que par chaque tic d'horloge. Pour s'assurer que toutes les étapes suivent l'ordre du pipeline, elles seront en mode veille immédiatement après leur création. Après cela, ces étapes vérifient constamment s'il y a un signal de réveil provenant de l'étape précédente. Une fois que chaque étape a terminé son traitement, elle réveille la prochaine étape, puis revient en mode d'attente jusqu'au signal suivant qui la réveillera. Pour pouvoir effectuer le déclenchement, des variables de condition et des mutex sont utilisés pour permettre la communication. Si un thread a besoin d'un autre thread pour le réveiller, il passera à l'état d'attente en verrouillant d'abord la variable de condition, puis en effectuant l'attente sur la variable de condition. Le thread ne reviendra à l'action qu'après la modification de la variable de condition. Le signal correspondant pour réveiller le thread est émis par un autre thread. Quand un thread doit en réveiller un autre, il verrouille la variable de condition et la modifie pour qu'elle corresponde à la condition requise pour l'autre thread, puis envoie le signal afin que l'autre thread sache qu'il est temps de se réveiller et de vérifier la condition. Et puis le thread libère le verrou pour que

d'autres puissent effectuer des opérations sur la même mémoire. À la fin, le thread qui a terminé son travail, et qui aura besoin d'un autre signal pour démarrer un nouveau cycle d'opérations, verrouille alors la variable de condition, modifie à nouveau la variable de condition, déverrouille la variable, puis recommence à attendre.

En combinant toutes ces fonctionnalités avec un pipeline logiciel, à l'exception de la première étape du pipeline, toutes les autres étapes du pipeline doivent passer en état d'attente après la création du thread. Et la première étape du pipeline décide de la fréquence à laquelle ces étapes du pipeline peuvent être déclenchées. La différence est qu'au lieu d'utiliser l'horloge pour permettre à chaque étape du pipeline de démarrer le mouvement suivant, c'est déclenchée uniquement par l'étape précédente, ce qui peut provoquer un brouillage car chaque étape du pipeline a un temps d'exécution différent, et le brouillage se produit généralement sur celui qui prend le plus de temps pour s'exécuter. Pour éviter le brouillage qui était considéré comme l'un des résultats des problèmes de variation temporelle, il suffit simplement de s'assurer que le temps d'exécution de chaque étape ne dépasse pas le temps de la fréquence du déclenchement à partir de la première étape du pipeline. Et la structure du pipeline pour la radio logicielle est illustrée à la figure 13.

Enfin, parlons de l'accélération fonctionelle. Dans la conclusion précédente, les étapes les plus longues sont le canal partagé et la génération de l'OFDM. Il est essentiel d'analyser quelle fonction consomme le plus de temps d'exécution au sein du canal partagé. Comme le montre la figure 5, en prenant la liaison descendante comme exemple, il existe un codage, un brouillage, QAM, un mappage de couche, un précodage et la génération de l'OFDM qui peuvent être la cible de l'accélération.

Dans la 5G, l'algorithme de codage utilise le contrôle de parité à faible densité (Low-Density Parity-Check, LDPC). Ce que fait LDPC, c'est de coder la chaîne de données en attachant une chaîne de bits de contrôle de parité à la fin de chaque bloc de données codé, où la génération des bits de contrôle de parité est créée par les données d'origine traversant une matrice creuse. Dans la norme 3GPP, LDPC prend en charge plusieurs tailles de matrices creuses où plus la taille de la matrice est large, plus le temps de traitement est long pour une même chaîne d'entrée en raison du nombre de bits de contrôle de parité à générer. Il existe deux matrices « Base Graph » (BG) qui ont des tailles de quarante-six fois soixante-huit pour BG1 et quarante-deux fois cinquante-deux pour BG2 pour le LDPC selon la norme 3GPP. Et l'expansion pour ces BG peut aller jusqu'à trois cent quatre-vingt-quatre, ce qui signifie que chaque nombre au BG se transformera en une matrice au niveau du bit avec une taille de facteur d'expansion multipliée par le facteur d'expansion. Quant au décodage, il utilise également la même matrice pour l'opération mais estime la chaîne de bits à travers le rapport log-vraisemblance (loglikelihood ratio, LLR). Le codage aussi bien que le décodage sont des opérations basées sur les blocs. Chaque bloc n'est pas lié aux autres, ce qui rend l'opération très répétitive et indépendante des données à travers les blocs. Étant donné que LDPC a toujours de grandes matrices de parité, l'opération matricielle prend du temps pour terminer un bloc. L'encodage et le décodage LDPC consomment à la fois du temps et des ressources. Il s'agit même des opérations les plus coûteuses en temps quand on teste tout le système en simulation. Le traitement matriciel basé sur des blocs et le long temps d'exécution en

Figure 13 – Pipeline radio logicielle

font des candidats idéals pour l'accélération fonctionnelle.

Ce que fait le brouillage, c'est réduire la possibilité que des données proches soient contaminées en même temps, ce qui rend l'information plus difficile à décoder ou même impossible à inverser. Pour ce faire, le bit actuel est lié à un couple spécifique de bits qui ont déjà traversé le brouilleur auparavant. Après avoir passé la séquence de bits à travers une transformation de type aléatoire, on obtient la séquence de départ pour le brouillage. Puisque l'entrée se présente sous la forme d'une chaîne de bits et que chaque bit de sortie est affecté par le bit d'entrée précédent, il n'est pas approprié d'effectuer le brouillage en parallèle en raison de son exécution séquentielle native.

Quant à QAM, il fait correspondre un groupe de bits à un ensemble spécifique d'amplitudes et d'angles où l'amplitude et l'angle sont décidés par le type de QAM. Le niveau pour QAM peut aller par exemple du taux de modulation le plus bas, un à un, la modulation par déplacement de phase binaire (Binary phase-shift keying, BPSK), pour transporter plusieurs bits avec un ensemble d'amplitudes et d'angles, comme illustré à la figure 6. Une fois le niveau QAM décidé, les données de la chaîne seront alors regroupées puis transposées sur l'ensemble angle-amplitude. Cela signifie qu'il n'y a pas de relation entre les groupes, ce qui facilite le traitement parallèle du fonctionnement QAM. Cependant, ce que fait QAM, c'est simplement mapper des ensembles de bits sur des ensembles d'amplitudes et d'angles, ce qui ne prend pas beaucoup de temps.

Enfin, c'est OFDM. Il est utilisé avant d'envoyer un signal aux antennes pour résoudre les problèmes d'ISI et de « delay spread » comme mentionné précédemment. Dans la 5G, la transformée de Fourier rapide (FFT) et la transformée de Fourier discrète inverse (IDFT) pour le fonctionnement OFDM ont jusqu'à quatre mille quatre-vingt-seize points, ce qui signifie qu'il y aura une matrice de taille quatre mille quatre-vingt-seize fois quatre mille quatre-vingt-seize impliquée dans l'opération. Le traitement OFDM est également une opération matricielle avec une complexité en  $O(n^2)$ . Il existe des moyens de simplifier l'opération, mais même avec un meilleur algorithme, on obtient toujours une complexité en O(nlogn). Comme il existe une taille maximale pour FFT et IDFT, la chaîne de données est séparée en groupes pour l'opération. Étant donné que la 5G utilise de multiples antennes, avoir toutes les données pour différentes antennes n'est pas efficace. La FFT et l'IDFT ont toutes deux un fonctionnement matriciel très complexe et le fonctionnement sur différentes antennes n'a aucune dépendance. Tout cela en font de bonnes candidates pour l'accélération.

Après avoir choisi le candidat pour l'accélération fonctionnelle, plusieurs méthodes existent pour réaliser l'accélération. La première consiste à avoir une accélération sur un CPU à plusieurs cœurs à l'aide de threads de travail. La seconde consiste à utiliser un matériel spécial pour effectuer le traitement (offloading). Et la troisième est d'avoir un jeu d'instructions spécial.

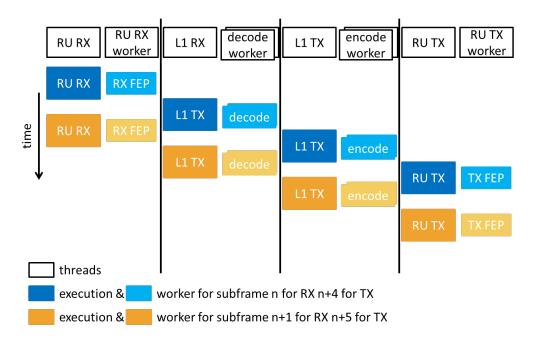

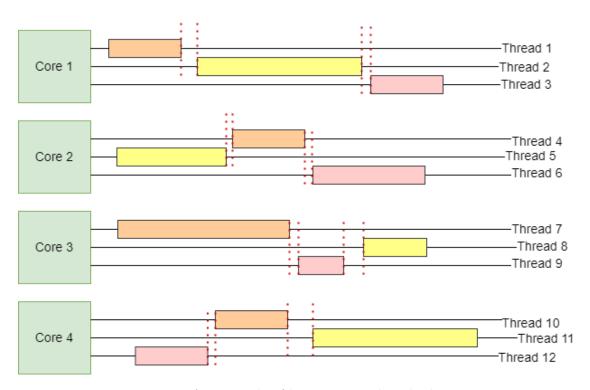

Pour l'accélération à l'aide de threads de travail, plusieurs threads de travail sont créés et utilisés par le thread d'origine qui est un thread dominant. Il contrôle les threads de travail qui traitent les données et les collecte à la fin du processus. C'est ainsi que le threading fonctionnel parallèle est utilisé. Ceux qui ont le fonctionnement de groupe, ce qui signifie qu'il n'y aura pas de dépendance au sein des groupes, pourraient alors être facilement séparés. Utiliser des threads de travail pour répartir la charge de travail pour

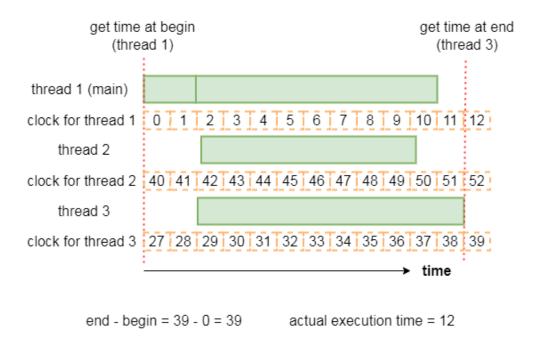

les processus les plus chronophages du pipeline est ce que nous voulons faire avec la radio logicielle temps réel. Comme mentionné précédemment, le codage et le décodage sont les goulots d'étranglement du traitement PHY. En analysant la façon dont les données sont gérées dans la fonction, il est clair que le codage et le décodage sont des opérations basées sur des blocs, ce qui signifie que l'on peut diviser quelques-uns des blocs en threads de travail pour obtenir du parallélisme. Le thread principal s'occupe des opérations communes avant l'opération principale, puis distribue une partie des données aux threads de travail qui ont des opérations identiques à exécuter en parallèle. Le temps d'exécution total sera le temps de fonctionnement commun plus le temps d'exécution du traitement des groupes de blocs qui est le temps d'exécution d'origine divisé par le nombre de threads de travail, plus enfin le temps d'attente des threads de travail terminant leur propre opération et signalant au thread principal que leur travail est terminé. En théorie, la meilleure performance que nous pouvons obtenir est le temps d'exécution des opérations communes et une part du temps d'exécution des processus parallèles.

Les processus DFT et IDFT sont tous deux des opérations basées sur des blocs et les données entre différentes antennes sont indépendantes. Cela rend le traitement séquentiel des différentes antennes inefficace. La parallélisation des traitements sur les antennes est l'une des façons de faire, en utilisant les threads correspondants pour effectuer les opérations IDFT et DFT par antenne, puis envoyer les données au fronthaul pour que l'antenne envoie le signal. En faisant cela, on passe du temps de traitement d'origine d'une antenne multiplié par le nombre d'antennes à peut-être juste un peu plus que le temps de traitement d'une antenne en raison de la surcharge due à la synchronisation. Le résultat de la combinaison de la structure du pipeline et des threads de travail est illustré à la figure 14.

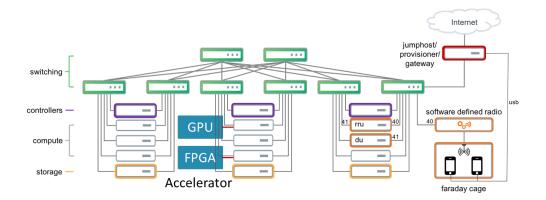

L'utilisation d'un accélérateur externe, par exemple un FPGA ou un GPU, est la deuxième option. La plupart du temps, l'accélérateur externe a sa propre manière d'organiser les données, donc avant d'envoyer des données à un accélérateur externe, les données doivent être réorganisées sous forme de blocs. Ce n'est qu'alors que l'on pourra envoyer les données pour un traitement parallèle et puis collecter les données une fois l'opération dans l'accélérateur externe terminée. L'accélérateur externe doit alors renvoyer les données à l'étape du pipeline. Les données renvoyées peuvent nécessiter un autre réarrangement pour l'étape suivante. Il y a plus de données qui sont échangées lors de l'utilisation de l'accélérateur externe, ce qui signifie que nous devons nous concentrer sur l'opération la plus longue. Ce qui suit va parler de l'utilisation du GPU comme accélérateur externe. Le GPU fait naturellement de la programmation parallèle, ce qui lui donne un avantage pour accélérer un traitement dupliqué. Et cela fait du GPU un bon candidat pour le codage et le décodage. Mais comme mentionné précédemment, toutes les données doivent être réorganisées puis envoyées au GPU pour qu'il puisse les traiter. En particulier dans les stations de base des centres de données, les données transmises vers et depuis le GPU créent une longue latence. Cela signifie que l'utilisation de bus normaux pour le transfert de données n'est pas suffisante. Il y a besoin de bus à haut débit, supérieur à 1 Gbit/s, en radio logicielle pour un centre de données 5G. Tout cela signifie que la latence créée par le transfert des données devra également être prise en compte. Bien que le GPU ait un support natif pour la programmation parallèle, il a

Figure 14 – Combiner les threads de travail et la structure du pipeline

une fréquence d'horloge plus lente, des cœurs plus simples, une mémoire partagée au sein d'un groupe de processeurs et plusieurs groupes de processeurs. Tous ces éléments rendent la programmation sur GPU plus difficile à concevoir et nécessitent plus d'efforts sur la conception parallèle.

La dernière technique d'accélération est d'utiliser un jeu d'instructions spécial. SIMD est l'abréviation de Single Instruction Multiple Data (Instruction Unique Données Multiples), ce qui montre déjà ses capacités de traitement parallèle natif de par son nom. Il s'agit d'un traitement parallèle au niveau de l'instruction. SIMD est utilisé pour traiter plusieurs variables à la fois. SIMD utilise l'idée d'avoir plusieurs opérations simples identiques opérant sur un grand vecteur avec une opération simple. Par exemple, l'opération d'addition de tous les éléments de « a » et « b », et de stockage du résultat dans « x » peut être transformée en un processus vectoriel « X = A + B ». C'est ainsi que SIMD fonctionne. SIMD prend en charge un groupe de données en y effectuant la même opération, par exemple ici une addition vectorielle. SIMD accélère en transformant une opération de boucle en une instruction opérant directement sur un vecteur. Cela raccourcit le temps d'exécution d'une boucle d'instructions au temps d'exécution d'une instruction SIMD.

Comme mentionné précédemment, il existe plusieurs endroits qui utilisent des blocs comme base de traitement et opèrent de manière répétée dans le traitement du signal. De nombreux traitements sont des opérations basées sur les bits. Le remplacement du code d'origine par un équivalent SIMD réduit considérablement le temps de fonctionnement pour le traitement de données de chaîne simples. Cela rend SIMD pratique pour accélérer considérablement le traitement. Partout où il y a une opération matricielle, il est possible

Figure 15 – La combinaison des threads de travail et de la structure du pipeline

de la transformer en plusieurs opérations vectorielles plutôt que d'utiliser une double boucle pour couvrir l'opération matricielle. En ce qui concerne la répétition d'opérations sur des données de chaîne, tant que l'opération elle-même n'entraîne pas de dépendance des données sur la chaîne de bits, il est également possible de dérouler l'opération en une opération vectorielle. Par exemple, LDPC est une opération matricielle qui peut être découpée en plusieurs processus vectoriels.

Pour SIMD, il y a plusieurs avantages et inconvénients. L'avantage le plus important que nous en tirons est de raccourcir considérablement le temps de traitement, ce qui compte beaucoup dans la radio logicielle temps réel. Pourtant, il y a encore des limites au SIMD. Il s'agit d'un jeu d'instructions spécial qui cible spécifiquement certains processeurs, ce qui signifie que la radio logicielle aura besoin de plusieurs jeux d'instructions SIMD correspondant aux différentes plates-formes prises en charge par le logiciel. Le jeu d'instructions SIMD ne prend en charge que les opérations simples, ce qui signifie que si l'opération est trop complexe à désassembler, elle ne peut pas utiliser SIMD pour s'exécuter. De plus, SIMD a des limites sur la longueur des données sur lesquelles il peut fonctionner. Cela signifie que si une donnée est plus longue que la taille des données SIMD, il faudra la séparer en plusieurs données pouvant tenir dans la taille des données SIMD pour pouvoir fonctionner. Le code SIMD est plus proche du code d'assemblage que du code C normal. Cela signifie qu'il est moins instinctif et plus difficile à comprendre. Il faut aussi transférer les données dans les registres spéciaux SIMD avant de pouvoir procéder. De plus, les données étant traitées par bloc, cela signifie que leur taille doit être multiple de la taille d'un bloc SIMD. Et comme il s'agit plus d'un code assembleur que d'un code C général, il est fortement dépendant de l'environnement ce qui rend difficile le changement de plate-forme.

Après avoir combiné toutes les fonctionnalités ci-dessus, on obtient une structure de radio logicielle comme illustré à la figure 15.

# Acknowledgements

# Contents

|   | Abs  | tract                                                                           | i   |

|---|------|---------------------------------------------------------------------------------|-----|

|   | Ack  | $oxed{	ext{nowledgements}}$                                                     | vii |

|   | Con  | tentsx                                                                          | ix  |

|   | List | of Figures                                                                      | XX  |

|   | List | of Tables                                                                       | xii |

|   |      | onyms                                                                           |     |

|   | Nota | ations                                                                          | 1   |

| 1 | Intr | roduction                                                                       | 1   |

|   | 1.1  | Software Defined Radio                                                          | 6   |

|   | 1.2  | 5G Systems and Implementation Technologies                                      | 7   |

|   | 1.3  | Motivation                                                                      | 10  |

| 2 | Soft | tware Optimized Real-time Processing for 5G systems                             | 11  |

|   | 2.1  | Related Work and State of the Art                                               | 11  |

|   |      | 2.1.1 Multi-threading for Parallelized Execution on Multi-Core Systems          | 12  |

|   |      | 2.1.2 Hardware Acceleration(FPGA/GPU)                                           | 13  |

|   |      | 2.1.3 SIMD/VLIW optimizations                                                   | 14  |

|   | 2.2  | Real-time SDR and Fronthaul Interface                                           | 15  |

|   | 2.3  | Challenges in Implementing Real-time SDR                                        | 16  |

|   | 2.4  | Considered Approach for Implementing Real-time SDR-base $5\mathrm{G}$ systems . | 16  |

| 3 | Fun  | actional Decomposition and Pipelining for 5G radio processing                   | 19  |

|   | 3.1  | 5G Physical-Layer Procedures                                                    | 20  |

|   | 3.2  | Proposed Pipelining Methods                                                     | 22  |

|   |      |                                                                                 | 23  |

|   |      | 3.2.2 Software Pipeline                                                         | 24  |

|   |      |                                                                                 | 27  |

| 4 | Acc  | eleration Methods for 5G Functional Blocks                                      | 29  |

|   | 4.1  | Acceleration Target Choice                                                      | 29  |

|   | 4 2  | Splitting Method                                                                | 34  |

| 6 | Con | nclusion and Future Work                                      | <b>5</b> 5 |

|---|-----|---------------------------------------------------------------|------------|

|   | 5.3 | Results of Performance Evaluation on multi-core x86 platforms | 45         |

|   | 5.2 | Performance Evaluation Methods                                | 42         |

|   | 5.1 | Testing Methods                                               | 41         |

| 5 | Imp | plementations Using OpenAirInterface                          | 39         |

|   | 4.3 | SIMD optimizations                                            | 37         |

|   |     |                                                               |            |

# List of Figures

| 3   | IMT-2020                                                                 |

|-----|--------------------------------------------------------------------------|

| 4   | Inter Symbol Interference (ISI) iii                                      |

| 5   | Inter Carrier Interference (ICI) iv                                      |

| 6   | Quadrature Amplitude Modulation (QAM) diagram example iv                 |

| 7   | Flux de procédure PHY pour la radio logicielle vi                        |

| 8   | Réponse du canal dans différents modes vi                                |

| 9   | Procédure pour l'exécution séquentielle radio logicielle vii             |

| 10  | Mappage des canaux - ShareTechNote viii                                  |

| 11  | Un exemple de structure de pipeline à trois étages ix                    |

| 12  | Risque                                                                   |

| 13  | Pipeline radio logicielle                                                |

| 14  | Combiner les threads de travail et la structure du pipeline xv           |

| 15  | La combinaison des threads de travail et de la structure du pipeline xvi |

| 1.1 | Internet seven layers from SystemZone                                    |

| 1.2 | Inter Symbol Interference                                                |

| 1.3 | Inter Symbol Interference                                                |

| 1.4 | Three dimension for 5G from IMT-2020                                     |

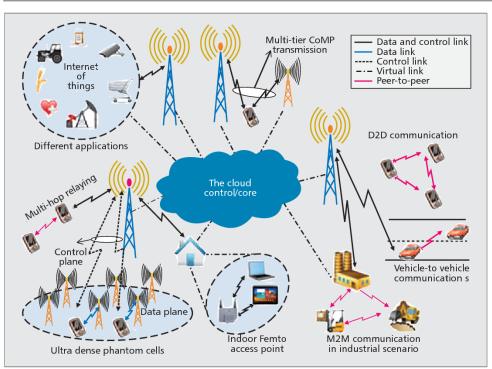

| 1.5 | SDR 5G network from IEEE [1]                                             |

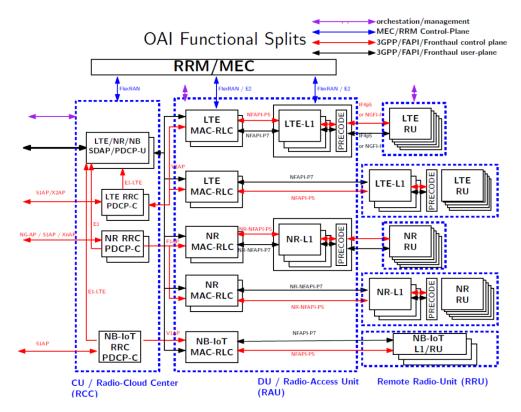

| 1.6 | OpenAirInterface Functional split                                        |

| 1.7 | Flow for Physical Layer                                                  |

| 2.1 | OpenAirInterface Functional split                                        |

| 2.2 | Hazard that might happen while using multi-thread                        |

| 2.3 | Four slot delay from received to send                                    |

| 2.4 | Data-center environment with FPGA/GPU accelerator                        |

| 3.1 | Consecutive execution for receive and transmit set                       |

| 3.2 | Channel mapping diagram from ShareTechNote                               |

| 3.3 | Physical layer flow with the functional split                            |

| 3.4 | Simplest pipeline example                                                |

| 3.5 | Hazard that might happen when using parallel programming 24              |

| 3.6 | Example of One of The Mutex Used in SDR                                  |

| 3.7 | Bit-wise mapping mask indicator                                          |

| 3.8 | Threads communication with mutex lock introduced                         |

| 3.9  | Pipeline structure works in timing aspect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | Resource grid for NR from ShareTechNote                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30 |

| 4.2  | Quadrature Amplitude Modulation (QAM) diagram example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 |

| 4.3  | OFDM effect on resource element for both time and frequency domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | from 5G Technology World                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34 |

| 4.4  | Including worker threads to the procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35 |

| 4.5  | Combing worker threads and pipline structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36 |

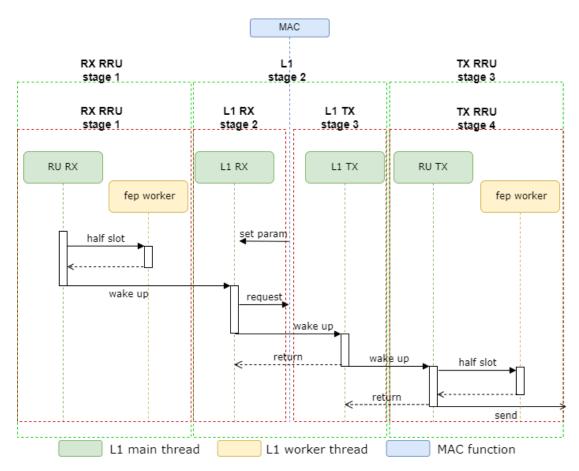

| 4.6  | The communication between threads when combining pipeline structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 1.0  | and worker threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37 |

|      | wild worker through the transfer of the transf | ٠. |

| 5.1  | The role that Operation System (OS) play                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40 |

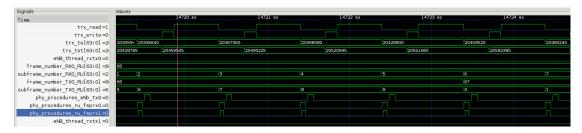

| 5.2  | Timing measurement on different threads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43 |

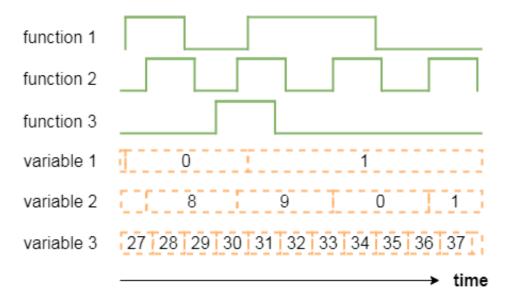

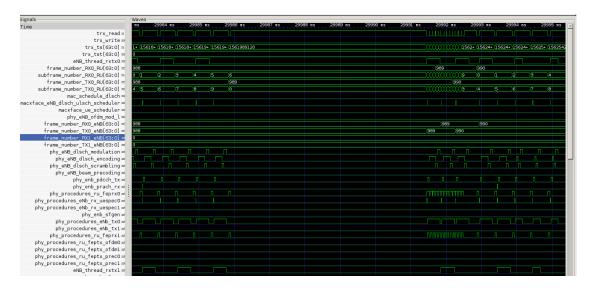

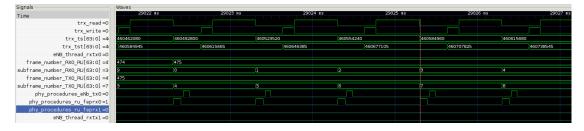

| 5.3  | VCD tracking for function and variable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44 |

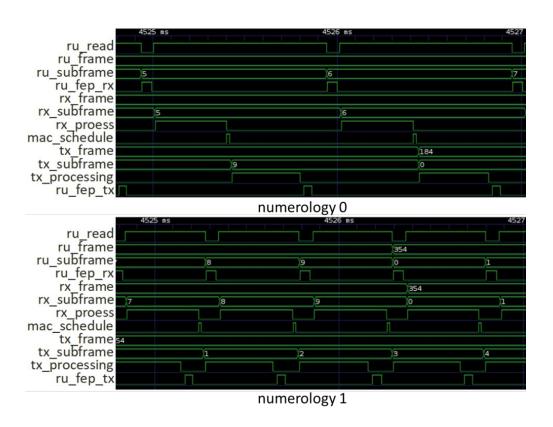

| 5.4  | VCD tracking for function and variable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46 |

| 5.5  | Two different pipeline split                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47 |

| 5.6  | Functions that is categorized in different acceleration group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47 |

| 5.7  | The ability of pipeline structure to recovery from a sudden data rush                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49 |