# Hardware Optimized Sample Rate Conversion for Software Defined Radio

Carina Schmidt-Knorreck, Raymond Knopp, \*Renaud Pacalet

Institute Eurecom, \*TELECOM ParisTech - Institute Eurecom 2229 route des Cretes, F-06904 Sophia-Antipolis Cedex - France Carina.Knorreck@eurecom.fr, Raymond.Knopp@eurecom.fr, Renaud.Pacalet@TELECOM-ParisTech.fr

Abstract— The evolution towards applications with increasing functionalities leads to the need of high flexible systems that support a high number of different standards while decreasing the required space consumption. Therefore a high configurable platform being able to handle different standards is needed. One main issue is the tradeoff between performance and space consumption. We present a generic, flexible and hardware optimized SRC architecture in the context of SDR, providing one architecture to process up to 8 different complex channels. The solution is based on bandlimited interpolation and allows processing by supporting a 1Hz resolution between the sampling rates.

Index Terms—SDR, SRC, Hardware Architecture, Open platforms for multistandard support, Baseband Processing, HW accelerators

### I. INTRODUCTION

In the past years, the number of different standards used in wireless communications (GSM, OFDM, WCDMA etc) has grown rapidly. New products deliver more functionalities to the users and merge already existing ones in only one advice. Today mobile phones, for instance, allow not only to make a phone call, but also to surf on the web or to listen to the radio. The evolution towards applications with increasing functionalities leads to the need of high flexible systems that support a high number of different standards while decreasing the required space consumption. Their architecture differs from standard to standard; due to different carrier frequencies, channel

Eurecom's Research is supported in part by its industrial partners: Swisscom, Thales, SFR, Orange France, Hitachi Europe, STMicroelectronics, Bouygues Telecom, Sharp, Cisco, BMW Group. The research work leading to this paper has also been partially supported by the European Commission under the ICT research network of excellence NEWCOM++ and by the project PLATA.

bandwidths and modulation schemes. The solution to this challenging task can be found in the concept of Software Defined Radio (SDR). By definition, SDR is a reconfigurable radio communication system that can be tuned to any frequency band and that can handle all the modulation schemes in a wide frequency range [6]. Furthermore high configurable platforms should not only provide a flexible hardware architecture but also shorter development cycles and better debugging capabilities.

The digital baseband processing platform being developed by Institute Eurecom and TELECOM Paris-Tech is a generic prototype architecture for SDR applications [3]. Its multimodal design supports almost all existing standards and allows an easy adaptation of future technologies without changing the HW/SW architecture. The partitioning between HW and SW follows a general cost-and-complexity versus speed trade-off. The main objective in design is to find the most flexible solution with highest performance and minimal space consumption. Furthermore it has to meet the throughput and the latency requirements of the computationally most intensive task. The relevant parameters of the design may differ between the standards and are managed by the software part that synchronizes the different processes on the platform.

One of the critical processing blocks in terms of performance and space consumption is the preprocessor that connects the external radio front end with the entire platform. In the context of this paper we focus on its most critical element - the fractional Sample Rate Converter (SRC), also called Retiming Filter (RTF). First the different requirements are listed in section II, before a short overview on the preprocessor is given (section III). Different existing solutions are examined in section IV and evaluated in terms of performance and space consumption. An architecture

based on one of those algorithms is presented in section V and the performance results are part of section VI. At the end possible extensions of the filter design are summed up in section VII.

### II. REQUIREMENTS

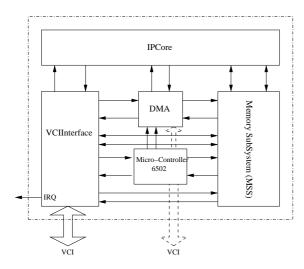

The requirements can be divided into two different groups. First the non-functional requirements due to the platform design, and second, the functional requirements related to sample rate conversion. From the platform perspective, the general architecture of the preprocessor is the same like for the other blocks for the digital baseband processing (Frontend Processor, Channel Decoder, etc). The standardized IP shell that can be seen in Figure 1 allows the reuse of most of the control and communication logic and an easy upgrading or replacement in the future. The architecture of the IP core and the Memory Subsystem depend on the functionality of each block while DMA, VCI Interface and Micro-Controller are designed globally.

Fig. 1. Standardized IP Shell

Another requirement results from the target architectures, first a Xilinx Virtex 5 LX330 FPGA and later a SoC. During synthesis, so called Extreme DSPs or DSP48E slices are invoked whenever possible. These elements speed up the design significantly and are not only used by the preprocessor but also by the front end processor for instance. As mentioned before, the design of the SRC has to be as simple as possible in order to minimize the required space consumption. This task is not that simple as due to the high bandwidth of the signal coming from the A/D converters the data rate will be very high. This leads easily to a

higher hardware complexity and a higher power consumption and results in a high number of DSP48E slices and accordingly to a cost intensive application. From the SRC perspective a generic design performing fractional up- and downsampling using the same underlying architecture is preferred. The whole design has to be configurable using a set of parameters that is handled by the SW control. The same SRC module is used for reception (RX), transmission (TX) and reception and transmission at the same time. From the platform perspective, the different channels processed by the SRC are executed in parallel. To fulfill this requirement, the speed of the SRC has to be higher than the speed of the other baseband processing blocks. To decrease the jitter one fixed master clock with low jitter is provided to the preprocessor. Thus the difference between the sampling rates has to be managed by the SRC itself. Performance has to be high and the SRC has to avoid aliasing.

#### III. PREPROCESSOR BLOCK

The preprocessor connects the external radio front end with the digital baseband processing platform. It has to ensure among others that the incoming and outgoing sample streams are modified in order to provide the data format and the sampling rate of the connected device as well as the sampling rate of the processed standard.

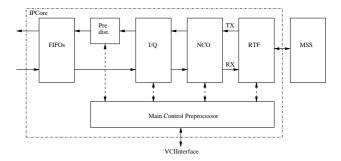

Apart from the interface with the external A/D and D/A converters, the preprocessor possesses a basic signal unit, a dual-port swing buffer, timing functions for framing and resynchronization and a sample synchronous interrupt generation. The signal processing unit is responsible for filtering, sample rate conversion and carrier frequency adjustment. Figure 2 gives an overview about the architecture of the preprocessor.

Fig. 2. Preprocessor Architecture

The incoming and outgoing samples are stored in FIFOs (interface A/D, D/A converters) and in the

memory subsystem (interface entire platform). This allows the realization of three different modes:

- 1) only reception

- 2) only transmission

- 3) reception and transmission in parallel

Up to 8 complex channels can be processed in parallel, each possessing a different set of parameters. The switch between two channels occurs after a fixed number of generated output samples and can be handled flexibly. The continuous processing of the preprocessor has to be guaranteed in order to to avoid a huge delay. This requires a control structure that stores / loads intermediate values into / from local RAMs. The necessary operations are performed in parallel to the main processing.

# IV. SAMPLE RATE CONVERTER FROM A HARDWARE PERSPECTIVE

### A. Comparison of Existing Solutions

In the architecture of SDR systems, SRCs are one of the critical and most demanding elements [1]. Compared to the other blocks on the baseband processing platform, the SRC is the most DSP heavy block that requires around 50% of the available DSP48E slices. In the past years, lots of different solutions for efficient SRC have already been presented, like for instance in [2], [5] or [9]. [12] has shown, that a solution based on polynomial interpolation in combination with CIC filters is the most efficient one in terms of performance. But the question in this context is, if the required space consumption justifies the obtained performance.

For an efficient implementation three factors must be considered. First the length of the lowpass filter that is used to avoid aliasing and thus the number of multiplications. Second, the amount of computation involved in the calculation of each new filter coefficient and third, the control structure.

The simplest SRC solution is the sample-and-hold method. The analog signal is sampled and the obtained value is hold afterwards. This solution is easy to implement and does not need many resources. But the obtained performance is too bad to use it in SDR applications.

Alternatively one could think about first increasing the sampling rate by zero insertion and then to decimate it. No fine interpolation stage is necessary; all effective filtering can be done in one filter at a low sampling rate. Unfortunately this solution requires a high space consumption as interpolation and decimation stage are not merged and as the filter grows for higher decimation factors. Fixing the size of the filter would be no feasible solution as aliasing effects occur and as inherent redundancy is removed.

A combination of a lowpass filter and A/D, D/A converters like presented in [10] is not appropriate for our design, either. This is due to the limited resources on the board and the choice of one single master clock to reduce the jitter and the phase noise respectively.

Remains the approach of interpolation in combination with the window method where an interpolation filter to calculate missing output samples or filter coefficients is combined with a lowpass filter to avoid aliasing ([8]). The performance depends on the number of stored filter coefficients and on the interpolation method. Using a higher order polynomial requires a higher computational effort and thus a higher space consumption. Calculating the filter coefficients in a recursive way would be an option. But to do so, the latency increases and further resources to calculate them are needed. To interpolate, different solutions are possible. The easiest solution is the nearestneighbor interpolation. The corresponding hardware structure is quite simple but the efficiency is very low. Using linear interpolation leads to a better performance with low space consumption. Good filter characteristics are possible but the filter coefficients need to be precomputed and stored in memory. A generalization of linear interpolation is the polynomial interpolation, which possesses a high efficiency ([7]). Compared to linear interpolation, the calculation of the interpolating polynomial is computationally expensive. Another disadvantage is Runge's phenomenon, which shows that the interpolation polynomial may oscillate wildly between the data points for higher order ones. The most hardware consuming interpolation methods are the Spline interpolation which avoids Runge's phenomenon by using piecewise defined polynomials and the Whittaker-Shannon interpolation which is only working for infinite sig-

As a mixture between linear interpolation and Whittaker-Shannon interpolation, [13] has introduced the concept of bandlimited interpolation. This method is easily implementable and can highly be optimized by minimizing the required hardware space. The same algorithm can be used for upsampling and downsampling. The filter coefficients have to be precomputed and stored in the memory subsystem.

### B. Presentation of the chosen Algorithm

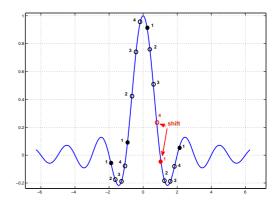

The solution that has finally been chosen is the above mentioned bandlimited interpolation. The filter is a combination of a FIR lowpass filter and a linear interpolation filter. The result is obtained by shifting signal samples under a windowed sinc function. The current moment in time represents the time instance under the peak of the sinc function. The output is a linear combination of the signal samples or of the corresponding filter coefficients, respectively. For more detailed information please refer to [13].

Having a look at the downsampling case, the sampling rate at the input, denoted  $F_1 = \frac{1}{T_1}$ , is increased to a sampling rate  $F_2 = \frac{1}{T_2}$ . Having a sampled signal  $x(nT_1)$  at the input of the SRC, its corresponding analog signal can be computed by

$$x(t) = \sum_{n} x(nT_1)g(t - nT_1),$$

(1)

where g(t) is a sinc function multiplied with the Kaiser window. To get the same signal at a different sampling rate this analog signal is expressed from its samples with timing  $T_2$ , namely

$$x(kT_2) = \sum_{n} x(nT_1)g(kT_2 - nT_1), \qquad (2)$$

where  $T_1$  and  $T_2$  have no specific relationship a priori. The sampling rate of the filter is  $T_3$  which means that the real filter function has to be expressed as  $g(nT_3)$ . For the downsampling case, the following term is valid:  $T_1 = MT_3$ . M is the oversampling factor for the sampled representation of the basis waveform g(t).

So we get

$$x(kT_2) = \sum_{n} x(nT_1)g(kT_2 - nMT_3)$$

(3)

As not all necessary filter coefficients are available right at the beginning a parameter k' has to be defined such that  $k'T_3 \leq kT_2 < (k'+1)T_3$ , or equivalently  $k' = \lfloor k\frac{T_2}{T_3} \rfloor$ . k' represents an existing filter coefficient while k represents a filter coefficient that has to be computed via linear interpolation.

So (3) can be approximated as

$$x(kT_2) \approx \sum_{n} x(nT_1)[(1-\alpha_k)g((k'-nM)T_3) + \alpha_k g((k'-nM+1)T_3)$$

(4)

with

$$\alpha_k = k \frac{T_2}{T_3} - k'. \tag{5}$$

To optimize the filter structure and to minimize the necessary hardware resources it is useful to have a polyphase representation of (4). One first has to define

$$k' = k''M + l_k \tag{6}$$

where  $l_k = k' \mod M$  and

$$g_{l_k}(n) = g((nM + l_k)T_3), l_k = 0, 1, \dots, M-1$$

(7)

with  $g_{l_k}(n)$  as the polyphase representation of the prototype filter g(t) and M as the number of FIR filters processing in parallel.

The approximation in (4) can now be written more simply as

$$x(kT_2) \approx \sum_{n} x(nT_1)[(1 - \alpha_k)g_{l_k}(k'' - n) + \alpha_k g_{(l_k+1)modM}(k'' - n + I(l_k = M - 1))]$$

(8)

with  $I(\cdot)$  as the unit-valued indicator function.

The derivation for the upsampling case is similar. The only difference is that  $T_1$  and  $T_2$  have to be exchanged.

### V. SRC ARCHITECTURE

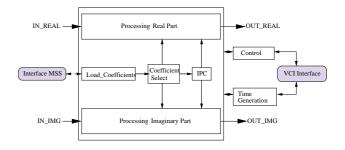

A simplified overview of the resulting hardware structure can be seen in Figure 3.

Fig. 3. Global Architecture of the SRC

The input samples are complex while the filter coefficients of the FIR filter are real. The filter coefficients are stored in the MSS and are first read in and then stored in registers before processing. Like the parameters they are provided by the modules InterpolationControl (IPC) and CoefficientSelect which are the same for the computation of the real and the imaginary output samples. Because of that it is adequate to have those modules only once in the system. All modules are working with the same clock. The difference between the sampling rate of the input samples and the sampling rate of the output samples has been realized using the module Time Generation which signals when a sample has to be written in the Registerbank and when an output sample has to be computed. Furthermore this module takes care of the communication with the connected blocks and is able to stop the whole filter if necessary.

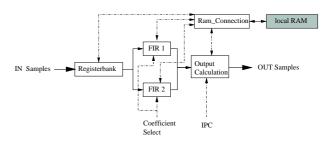

Hardware resources are saved in different ways: First, only four filters of the polyphase filter bank are implemented, two for the real and two for the imaginary part.

Apart from that the filter coefficients are highly optimized. In Figure 4 some ideal filter coefficients and their distribution over a polyphase filter bank using four filters is shown. Per filter processing, two consecutive filters are used. Normally the input samples of the two filters are the same, except for the case when the fourth and the first filter are used. In this case, the input samples of filter one have to be right shifted by one sample. Considering an implementation in hardware this would introduce a complexity that can be avoided. Having a look at the filter coefficients one can see that the coefficients of filter one are composed of one 1 and zeros otherwise. Thus it is sufficient to change only the value of two filter coefficients to produce a shift of the coefficients to the left. These two values can be hard coded in the architecture. Furthermore a periodicity can be observed that reduces the number of coefficients that have to be stored in memory by almost 29%.

4 complex channels (or 8 real channel respectively) can be processed in parallel per direction, which means that finally 16 real channels can be processed at the same time. For the purpose of not loosing any information when switching between them, the context of all SRC registers has to be stored in two local RAMs. Per module, two register sets are described. When a switch has to be performed, the old values are stored starting from a given address in the local RAM before the next channel to be processed is loaded.

Fig. 4. Filter Coefficient Distribution for an Ideal Lowpass Filter

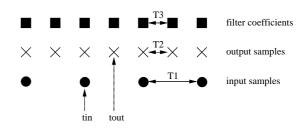

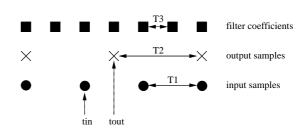

In the system of the SRC one can distinguish between different time domains: the time distance between the input samples (T1), the time distance between the output samples (T2) and the time distance between the filter coefficients (T3). The relation of these times depends on the mode. When upsampling, more output samples are computed than input samples exist while for downsampling the relation is the other way around.

The bit sizes of the times are set to 70 bit resulting from the required 1Hz resolution for the frequency range  $3 \text{ MHz} \le f \le 61.44 \text{ MHz}$ .

Fig. 5. Time Relations - Upsampling

Fig. 6. Time Relations - Downsampling

The maximum possible size of the filter is M=8 filters in the polyphase filter bank, each with 19 filter coefficients a 16 bit. The bit size could be increased to 25 bit without increasing the number of DSP48E slices. But simulations have shown, that the perfor-

mance gain is negligible. Possible degrees of freedom are the calculation of the filter coefficients or M, that could easily increased to 16 or 32 bit. For all other parameters the space consumption would increase significantly.

# A. Example: Processing of Four Channels Simultaneously

In this example four different channels are processed in parallel. The distribution could be 2 channels in TX and 2 channels in RX but one could also imagine 4 channel in TX or RX. The scheduling of the SRC would be the same. The four channels are processed one after another. If a channel is executed for the first time, the modules of the SRC have to be synchronized: first the filter coefficients are loaded and stored in local registers. Then the blocks IPC and Registerbank are enabled till they produce their first result and not till then the whole SRC is activated. In Figure 7 the scheduling is described. When for instance channel 2 is executed, the content of the previous channel, channel 1, is stored in a local RAM and the content of the next channel, channel 3, is loaded. As soon as the load process is finished a channel switch can be performed and channel 3 is executed without any delay.

Fig. 7. Channel Scheduling

### VI. RESULTS

### A. Performance Results

The maximum possible SINR is limited by the A/D and D/A converter performance. In transmission / reception the resolution is 14 / 12 bit which corresponds to a maximum SINR of 86.04 dB / 74 dB ([4]). Tests with different sinusoidal and sweep signals have shown, that this performance can easily be reached with a filter size of 8 times 19 filter coefficients if no interpolation is needed. In case of interpolation, the SINR depends on the ratio between the sampling frequencies, the oversampling factor of the input signal and the input signal itself. For an exemplary sinusoidal signal defined as  $y(x) = \frac{1}{4}sin(x') + sin(\frac{x'}{3}) + sin(\frac{x'}{2}) + cos(x')$  with  $x' = 2\pi f x$  the following results are obtained:

| mode         | factor | SINR     |

|--------------|--------|----------|

| upsampling   | 1.45   | 80.12 dB |

| upsampling   | 2      | 86 dB    |

| downsampling | 4.3    | 73.8 dB  |

| downsampling | 5      | 74 dB    |

When a white gaussian noise signal is used as input signal, the SINR can be obtained by evaluating the Power Spectral Density (PDS). Before processing the SRC, the input signal has to be lowpass filtered and oversampled. The SINR of the resulting signal has to be higher than the limiting factor by the A/D and D/A converters. Upsampling by a factor of 2.5 results in a SINR of around 82 dB while the SINR is very close to the maximum if no interpolation is needed.

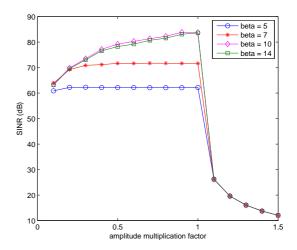

Apart from the number of filters in the polyphase filter bank the only adjustable parameter is the calculation of the filter coefficients. Different SINR values for the same basis waveform are obtained by changing the  $\beta$  parameter of the Kaiser window. Figure 8 shows how the SINR changes for different values of  $\beta$ . The input signal is a simple sinusoid.

Fig. 8. SINR Performance for Changing Beta

## B. Synthesis Results

In the following, synthesis results for a filter size of 8 x 19 filter coefficients are given. The target architecture is a Xilinx Virtex 5 LX330. For a clock frequency of 250MHz, the obtained frequency of the SRC is 167.73 MHz.

| Resource    | Used  | Avail. | Utilization |

|-------------|-------|--------|-------------|

| Funct. Gen. | 31801 | 207350 | 15.34%      |

| CLB         | 7951  | 51840  | 15.34%      |

| Dffs        | 20017 | 209760 | 9.54%       |

| Block RAMs  | 4     | 288    | 1.39%       |

| DSP48Es     | 82    | 192    | 42.71%      |

### VII. EXTENSION OF THE CURRENT DESIGN

The performance of the proposed SRC is the higher, the higher the sampling frequency of the incoming signal samples and the smaller the ratio between the sampling rates. For higher ratios, different extensions of the current design are possible. When upsampling, one common way is to add CIC filters to upsample the integer part before the fractional one ([14]). Thanks to the proposed SRC the final size of the resulting architecture would still be suitable for the target technology. Alternatively the presented SRC could be processed several times, but the introduced delay would be too high so that a parallel processing of the SRC from the other block's point of view is no longer guaranteed.

When downsampling one possible solution is a registerbank in which each register is addressable. Thanks to this structure a small program could be used to write the signal samples for the next processing into the registerbank. The latency of such a system would be smaller than the latency of a system where the samples are shifted one after another into the registerbank till the next output sample can be computed.

# VIII. CONCLUSION

In this article we have proposed a simple reconfigurable architecture for a sample rate converter, that is able to deal with almost all existing wireless communication standards. An analysis of existing solution has been accomplished from a hardware point of view. Our main concern was to find the algorithm with the highest performance but given a limited space consumption. As a result, a solution based on bandlimited interpolation in combination with Whittaker-Shannon interpolation has been presented.

The obtained algorithm performs resampling at a frequency of 167.73 MHz and supports a 1Hz resolution between the sampling frequencies. Furthermore possible extensions to the current filter design have been presented. Determining in detail their performance differences is part of our future work.

### REFERENCES

- Wajih A. Abu-Al-Saud, Gordon L. Stueber, "Efficient Sample Rate Conversion for Software Radio Systems", *IEEE Transactions of Signal Processing*, Vol 54, No. 3, March 2006

- [2] Ronald E. Crochiere, Lawrence R. Rabiner, "Interpolation and Decimation of Digital Signals", *Proceedings of the IEEE*, Vol. 69, No.3, March 1981

- [3] Najam-ul-Islam Muhammad, Rizwan Rasheed, Renaud Pacalet, Raymond Knopp and Karim Khalfallah, "Flexible Baseband Architecture for Future Wireless Systems", 11th EUROMICRO Conference on Digital System Design Architectures, 2008

- [4] Allen Gersho, Robert M. Gay, "Vector quantization and signal compression", Springer International Series in Engineering and Computer SScience

- [5] Tim Hentschel and Gerhard Fettweis, "Sample Rate Conversion for Software Radio", *IEEE Communications Magazine*, 38(8):142-150, August 2000

- [6] J.Mitola, "The Software Radio Architecture", *IEEE Commun. Mag.*, vol. 33, no 5, May 1995, pp.26-38

- [7] Alan V. Oppenheimer, Ronald W. Schaefer, John R. Ruck, "Discrete-Time Signal Processing", Second Edition, Prentice Hall

- [8] John G. Proakis, Dimitris G. Manolakis, "Digital Signal Processing; Principles, Algorithms and Applications", Fourth Edition, Prentice Hall

- [9] Tor A. Ramstad, "Sample-Rate conversion for arbitrary ratios", IEEE International Conference on Acoustics, Speech and Signal Processing, 1982

- [10] Tapio Saramki, Tapani Ritoniemi, "An efficient Approach for Conversion between arbitrary Sampling Frequencies", IEEE Internat. Symposium on Circuits and Systems, 1996, ISACS '96

- [11] Ali Shahed hagh ghadam, Markku Renfors, "Farrow Structure Interpolators Based on Even Order Shaped Lagrange Polynomials", *Proceedings of the 3rd Internat. Symposium on Image and Signals Processing and Analysis*, 2003

- [12] Faheem Sheikh, Shahid Masud, "Sample rate conversion filter design for multi-standard software radios", *Digital Signal Processing*, doi:10.1016/j.dsp.2009.04.014, 2009

- [13] Julius O. Smith, Phil Gossett, "A Flexible Sampling-Rate Conversion Method", *IEEE International Conference on ICASSP*, 1984

- [14] Tianqi Wang, Cheng Li, "Sample Rate Conversion Technology in Software Defined Radio", *Canadian Conference on Electrical and Computer Engineering*, 2006. CCECE '06.